PX4 Reference Flight Controller Design

The PX4 reference design is the Pixhawk series of flight controllers. First released in 2011, this design is now in its 5th generation (with the 6th generation board design in progress).

Binary Compatibility

All boards manufactured to a particular design are expected to be binary compatible (i.e. can run the same firmware). From 2018 we will offer a binary compatibility test suite that will allow us to verify and certify this compatibility.

FMU generations 1-3 were designed as open hardware, while FMU generations 4 and 5 provided only pinout and power supply specifications (schematics were created by individual manufacturers). In order to better ensure compatibility, FMUv6 and onward will return to a complete reference design model.

Reference Design Generations

- FMUv1: Development board (STM32F407, 128 KB RAM, 1MB flash, schematics) (no longer supported by PX4)

- FMUv2: Pixhawk (STM32F427, 168 MHz, 192 KB RAM, 1MB flash, schematics)

- FMUv3: Pixhawk variants with 2MB flash (3DR Pixhawk 2 (Solo), Hex Pixhawk 2.1, Holybro Pixfalcon, 3DR Pixhawk Mini, STM32F427, 168 MHz, 256 KB RAM, 2 MB flash, schematics)

- FMUv4: Pixracer (STM32F427, 168 MHz, 256 KB RAM, 2 MB flash, pinout)

- FMUv4 PRO: Drotek Pixhawk 3 PRO (STM32F469, 180 MHz, 384 KB RAM, 2 MB flash, pinout)

- FMUv5: Holybro Pixhawk 4 (STM32F765, 216 MHz, 512 KB RAM, 2 MB flash, pinout)

- FMUv6: work in progress, final name TBD, variant 6s (STM32H7, 400 MHz, 2 MB RAM, 2 MB flash) and variant 6i (i.MX RT1050, 600 MHz, 512 KB RAM, external flash)

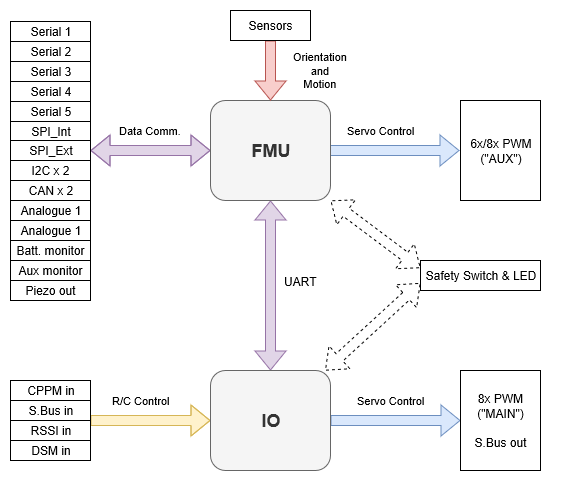

Main/IO Function Breakdown

The diagram below shows the division of bus and functional responsibilities between the FMU and I/O boards in a Pixhawk-series flight controller (the boards are incorporated into a single physical module).

Some Pixhawk-series controllers are built without the I/O board in order to reduce space or complexity, or to better address certain board use-cases. In this case the I/O driver is not started.

INFO

Manufacturer flight controller variants without an I/O board are often named as a "diminutive" of a version that includes the I/O board: e.g. Pixhawk 4 Mini, _CUAV v5 nano.

Build targets that must run on flight controllers with an I/O board map the FMU outputs to AUX and the I/0 outputs to MAIN (see diagram above). If the target is run on hardware where I/O board is not present or has been disabled, the PWM MAIN outputs will not be present. You might see this, for example, by running px4_fmu-v5_default on Pixhawk 4 (with IO) and Pixhawk 4 Mini (without I/O).

WARNING

On Pixhawk 4 Mini this results in a mismatch between the MAIN label screenprinted on the flight controller and the AUX bus shown during Actuator Configuration.

that if a build target is only ever intended to run on a flight controller that does not have an I/0 board, then the FMU outputs are mapped to MAIN (for example, the px4_fmu-v4_default target for Pixracer).

PX4 PWM outputs are mapped to either MAIN or AUX ports in Actuator Configuration.