PX4 参考飞行控制器设计

The PX4 reference design is the Pixhawk series of flight controllers. First released in 2011, this design is now in its 5th generation (with the 6th generation board design in progress).

二进制兼容性

所有按照特定设计制造的主板预计与二进制兼容(即可以运行相同的固件)。 从2018年起,我们将提供一个二进制兼容性测试套件,使我们能够验证兼容性。

第1-3代 FMU 设计用于开源硬件,但到了第4-5代只提供 pin 输出引脚和供电规格(原理图由个人开发者生成)。 为了可以更好的确保兼容性,FMUv6 及更新的版本重新提供完整的设计模型。

参考设计迭代:

- FMUv1: Development board (STM32F407, 128 KB RAM, 1MB flash, schematics) (no longer supported by PX4)

- FMUv2: Pixhawk (STM32F427, 168 MHz, 192 KB RAM, 1MB flash, schematics)

- FMUv3: Pixhawk variants with 2MB flash (3DR Pixhawk 2 (Solo), Hex Pixhawk 2.1, Holybro Pixfalcon, 3DR Pixhawk Mini, STM32F427, 168 MHz, 256 KB RAM, 2 MB flash, schematics)

- FMUv4: Pixracer (STM32F427, 168 MHz, 256 KB RAM, 2 MB flash, pinout)

- FMUv4 PRO: Drotek Pixhawk 3 PRO (STM32F469, 180 MHz, 384 KB RAM, 2 MB flash, pinout)

- FMUv5: Holybro Pixhawk 4 (STM32F765, 216 MHz, 512 KB RAM, 2 MB flash, pinout)

- FMUv5X: (Multiple Products) (STM32F765, 400 MHz, 512KB RAM, 2 MB flash) (standard)

- FMUv6X: (Multiple Products) (STM32H753, 480 MHz, 1 MB RAM, 2 MB flash) and variant 6i (i.MX RT1050, 600 MHz, 512 KB RAM, external flash) (standard)

- FMUv6C: (Multiple Products) (STM32H743V, 480 MHz, 1 MB RAM, 2 MB flash) (standard)

- FMUv6U: (Multiple Products) (STM32H753, 400 MHz, 1 MB RAM, 2 MB flash) (standard)

- FMUv6X-RT: (Multiple Products) (NXP i.MX RT1176, 32 Bit Arm® Cortex®-M7, 1GHz 32 Bit Arm® Cortex®-M4, 400MHz secondary core, 2 MB RAM, 64 MB flash) and variant 6i (i.MX RT1050, 600 MHz, 512 KB RAM, external flash) (standard)

Starting with FMUv5X all new standards are published on GitHub under Pixhawk/Pixhawk-Standards. See Pixhawk.org for more info.

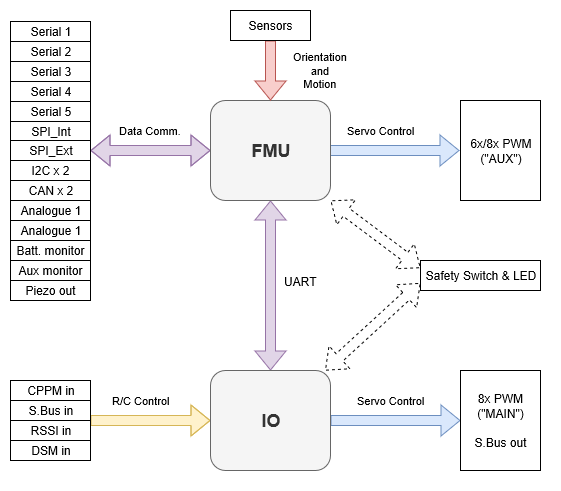

Main/IO 功能分解

下图展示了在Pixhawk系列飞行控制器(这些板被合并进一个单独的物理模块中)中 FMU 和 I/O 板之间总线和功能的职能划分。

一些Pixhawk系列控制器为了减少空间或复杂性,或者更好解决使用问题,没有通过I/O板构建。 In this case the I/O driver is not started.

INFO

Manufacturer flight controller variants without an I/O board are often named as a "diminutive" of a version that includes the I/O board: e.g. Pixhawk 4 Mini, _CUAV v5 nano.

Build targets that must run on flight controllers with an I/O board map the FMU outputs to AUX and the I/0 outputs to MAIN (see diagram above). If the target is run on hardware where I/O board is not present or has been disabled, the PWM MAIN outputs will not be present. You might see this, for example, by running px4_fmu-v5_default on Pixhawk 4 (with IO) and Pixhawk 4 Mini (without I/O).

WARNING

On Pixhawk 4 Mini this results in a mismatch between the MAIN label screenprinted on the flight controller and the AUX bus shown during Actuator Configuration.

that if a build target is only ever intended to run on a flight controller that does not have an I/0 board, then the FMU outputs are mapped to MAIN (for example, the px4_fmu-v4_default target for Pixracer).

PX4 PWM outputs are mapped to either MAIN or AUX ports in Actuator Configuration.